# 93448 VISOPLANAR SCHOTTKY TTL MEMORY 512×8-BIT PROGRAMMABLE READ ONLY MEMORY

0/077/

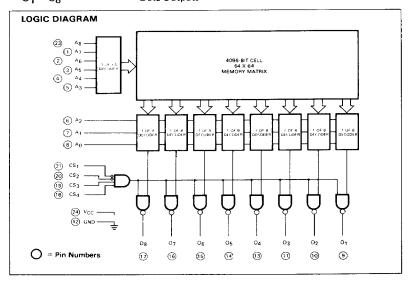

**DESCRIPTION** – The 93448 is a fully decoded 4096-bit field Programmable ROM organized 512 words by eight bits per word. The 93448 has 3-state outputs. The device is enabled when  $\overline{\text{CS}}_1$  and  $\overline{\text{CS}}_2$  are LOW and CS<sub>3</sub> and CS<sub>4</sub> are HIGH. The 93448 is supplied with all bits stored as logic "1"s and may be programmed to logic "0"s by following the field programming procedure.

- FULL MIL AND COMMERCIAL RANGES

- FIELD PROGRAMMABLE

- ORGANIZATION 512 WORDS X 8 BITS

- 3-STATE OUTPUTS

- FULLY DECODED ON-CHIP ADDRESS DECODER AND BUFFER

- CHIP SELECT INPUTS PROVIDE EASY MEMORY EXPANSION

- WIRED-OR CAPABILITY

- STANDARD 24-PIN DUAL IN-LINE PACKAGE

- NICHROME FUSE LINKS FOR HIGH RELIABILITY

- REPLACES TWO 256 X 8 PROMs DOUBLE DENSITY WITH SAME SPACE AND POWER

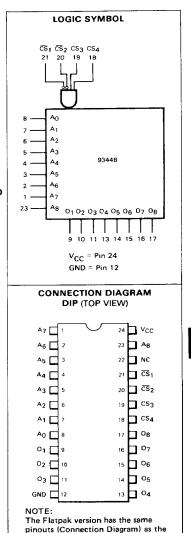

# PIN NAMES

$\frac{A_0 - A_8}{CS_1, CS_2, CS_3, CS_4}$   $O_1 - O_8$

Address Inputs Chip Select Inputs Data Outputs

Dual In-Line Package.

7-135

# FAIRCHILD ISOPLANAR SCHOTTKY TTL MEMORY • 93448

#### ABSOLUTE MAXIMUM RATINGS

Storage Temperature

Temperature (Ambient) Under Bias

V<sub>CC</sub>

Input Voltage

Current into Output Terminal

Output Voltages

-65°C to +150°C -55°C to +125°C -0.5 V to +7.0 V -0.5 V to +5.5 V 100 mA -0.5 V to 4.0 V

#### **GUARANTEED OPERATING RANGES**

| PART NUMBERS  | s      | AMBIENT |        |                 |

|---------------|--------|---------|--------|-----------------|

| TANT NOWIBERS | MIN    | TYP     | MAX    | TEMPERATURE     |

| 93448XC-      | 4.75 V | 5.0 V   | 5.25 V | 0°C to +75°C    |

| 93448XM       | 4.50 V | 5.0 V   | 5.50 V | -55°C to +125°C |

X = package type; F for Flatpak, D for Ceramic Dip, P for Plastic Dip. See Packaging Information Section for packages available on this product.

FUNCTIONAL DESCRIPTION — The 93448 is a bipolar field Programmable Read Only Memory (PROM) organized 512 words by eight bits per word. The 93448 has 3-state outputs which provide active <u>pull-ups</u> when enabled and high output impedance when disabled. Chip Select for both devices follows the logic equation:  $\overline{\text{CS}}_1 \bullet \overline{\text{CS}}_2 \bullet \text{CS}_3 \bullet \text{CS}_4 = \text{CS}$ ; i.e., if  $\overline{\text{CS}}_1$  and  $\overline{\text{CS}}_2$  are both active LOW and  $\overline{\text{CS}}_3$  and  $\overline{\text{CS}}_4$  are both active HIGH, all eight outputs are enabled; for any other condition all eight outputs are disabled.

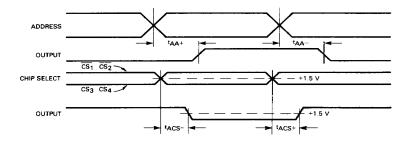

The read function is identical to that of a conventional bipolar ROM. That is, a binary address is applied to the  $A_0$  through  $A_8$  inputs, the chip is selected, and data is valid at the outputs after  $t_{AA}$  nanoseconds.

Programming (selectively opening nichrome fuse links) is accomplished by following the procedures in Chapter 6, page 6-14.

DC CHARACTERISTICS: Over guaranteed operating ranges unless otherwise note.

|                  |                                                                  | LIMITS |                 |              |          |                                                                                                                    |  |

|------------------|------------------------------------------------------------------|--------|-----------------|--------------|----------|--------------------------------------------------------------------------------------------------------------------|--|

| SYMBOL           | CHARACTERISTIC                                                   | MIN    | TYP<br>(Note 1) | MAX          | UNITS    | CONDITIONS                                                                                                         |  |

| v <sub>OL</sub>  | Output LOW Voltage                                               |        | 0.30            | 0.45         | V        | V <sub>CC</sub> = MIN, I <sub>OL</sub> = 16 mA<br>A <sub>0</sub> = +10.8 V, A <sub>1</sub> - A <sub>8</sub> = HIGH |  |

| v <sub>OH</sub>  | Output HIGH Voltage                                              | 2.4    |                 |              | V        | V <sub>CC</sub> = MIN, I <sub>OH</sub> = -2.0 mA                                                                   |  |

| l <sub>off</sub> | Output Leakage Current for HIGH<br>Impedance State               |        |                 | 50<br>-50    | μΑ<br>μΑ | V <sub>OH</sub> = 2.4 V<br>V <sub>OL</sub> = 0.4 V 0°C to +75°C                                                    |  |

| l <sub>off</sub> | Output Leakage Current for HIGH<br>Impedance State               |        |                 | 100<br>-50   | μΑ<br>μΑ | V <sub>OH</sub> = 2.4 V<br>V <sub>OL</sub> = 0.4 V -55°C to +125°C                                                 |  |

| $v_{IH}$         | Input HIGH Voltage                                               | 2.0    |                 |              | V        | Guaranteed Input HIGH Voltage for All Input                                                                        |  |

| V <sub>IL</sub>  | Input LOW Voltage                                                |        |                 | 0.8          | V        | Guaranteed Input LOW Voltage for All Inputs                                                                        |  |

| lF               | Input LOW Current IFA (Address Inputs) IFCS (Chip Select Inputs) |        | -160<br>-160    | -250<br>-250 | μA<br>μA | V <sub>CC</sub> = MAX, V <sub>F</sub> = 0.45 V                                                                     |  |

| I <sub>R</sub>   | Input HIGH Current IRA (Address Inputs) IRCS (Chip Select Input) |        |                 | 40<br>40     | μA<br>μA | V <sub>CC</sub> = MAX, V <sub>R</sub> = 2.4 V                                                                      |  |

| lcc              | Power Supply Current                                             |        | 130             | 175          | mA       | V <sub>CC</sub> = MAX, Outputs Open<br>Inputs Grounded and Chip Selected                                           |  |

| co               | Output Capacitance                                               |        | 7               |              | pF       | V <sub>CC</sub> = 5.0 V, V <sub>O</sub> = 4.0 V, f = 1.0 MHz                                                       |  |

| CIN              | Input Capacitance                                                |        | 4               |              | pF       | V <sub>CC</sub> = 5.0 V, V <sub>O</sub> = 4.0 V, f = 1.0 MHz                                                       |  |

| v <sub>c</sub>   | Input Clamp Diode Voltage                                        |        |                 | -1.2         | V        | V <sub>CC</sub> = MIN, I <sub>Δ</sub> = -18 mA                                                                     |  |

| SYMBOL                               | CHARACTERISTIC                | LIMITS |                 |          |          |                                    |

|--------------------------------------|-------------------------------|--------|-----------------|----------|----------|------------------------------------|

|                                      |                               | MIN    | TYP<br>(Note 1) | MAX      | UNITS    | CONDITIONS                         |

| <sup>t</sup> AA-<br><sup>t</sup> AA+ | Address to Output Access Time |        | 35<br>35        | 55<br>55 | ns<br>ns | See Waveforms<br>and Test Circuits |

| tACS-                                | Chip Select Access Time       |        | 15<br>15        | 25<br>25 | ns<br>ns |                                    |

AC CHARACTERISTICS:  $T_A = -55^{\circ}C$  to  $+125^{\circ}C$ ,  $V_{CC} = 5.0 \text{ V} \pm 10\%$

| SYMBOL                                 | CHARACTERISTIC                | LIMITS |                 |          |          |                   |  |

|----------------------------------------|-------------------------------|--------|-----------------|----------|----------|-------------------|--|

|                                        |                               | MIN    | TYP<br>(Note 1) | MAX      | UNITS    | CONDITIONS        |  |

| ************************************** | Address to Output Access Time |        | 35<br>35        | 70<br>70 | ns<br>ns | See Waveforms     |  |

| tACS-                                  | Chip Select Access Time       |        | 15<br>15        | 30<br>30 | ns<br>ns | and Test Circuits |  |

Note (1): Typical values are at  $V_{CC} = 5.0 \text{ V}$ , 5.0 V,  $+25^{\circ}\text{C}$  and max loading.

### SWITCHING WAVEFORMS

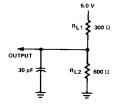

## SWITCHING TEST OUTPUT LOAD

15 mA Load

Fig. 1