# 4096-WORD BY 8-BIT READ-ONLY MEMORY

PIN NOMENCLATURE

Data Out

Ground

Chip Select

5-V Supply

Address inputs

or Chip Select

Chip Enable/Power Down

MAY 1977 - REVISED NOVEMBER 1985

| • | 4096 X 8 Organization                                                                  | N PACKAGE                                                                             |

|---|----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

| • | All Inputs and Outputs TTL Compatible                                                  | (TOP VIEW)                                                                            |

| • | Fully Static (No Clocks, No Refresh)                                                   | A7 []1 \(\times_{24}\) \(\nabla_{CC}\) \(A6 \) \(\frac{1}{2} \) \(23 \) \(A8\) \(A8\) |

| • | Single 5-V Power Supply                                                                | A5 📑 3 22 🖺 A9                                                                        |

| • | Maximum Access Time from Address TMS4732-15 150 ns TMS4732-20 200 ns TMS4732-25 250 ns | A4                                                                                    |

| • | Pin-Compatible with TMS2532 EPROM                                                      | Q1 9 16 Q7                                                                            |

| • | Optional Power Down or Chip Select                                                     | Q2 []10 15 Q6                                                                         |

Flexibility **Worst Case Active Power Dissipation**

Two Output-Enable Controls for Chip Select

Worst Case Standby Power Dissipation . . . 82.5 mW

#### description

. . . 330 mW

The TMS4732 is a 32,768-bit read-only memory organized as 4,096 words of 8-bit length. This makes the TMS4732 ideal for microprocessorbased systems. The device is fabricated using N-channel self-aligned silicon-gate technology for high speed and simple interface with bipolar and CMOS circuits.

The TMS4732 is fully compatible with Series 74, 74S, or 74LS TTL and CMOS logic. The data

outputs are three state for OR-tying multiple devices on a common bus. Pins 20 and 21 are mask programmable, providing additional system flexibility. The data at the outputs is always available during a read cycle. It is not dependent on external clocking of pins 20 and 21.

A0-A11

Q1-Q8

\$1/\$1

V<sub>C</sub>C

٧ss

E/E/S2/S2

This ROM is supplied in a 24-pin dual-in-line plastic (N suffix) package designed for insertion in mountinghole rows on 15,24-mm (600-mil) centers. The device is designed for operation from 0°C to 70°C.

#### operation

#### address (A0-A11)

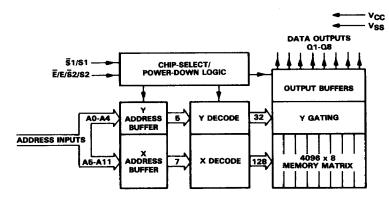

The address-valid interval determines the device cycle time. The 12-bit positive-logic address is decoded on chip to select one of 4096 words of 8-bit length in the memory array. A0 is the least-significant bit and A11 the most-significant bit of the word address.

# chip selects (\$\overline{S}1 or \$1 and \$\overline{S}2 or \$2)

Each of these pins can be programmed during mask fabrication to be active with either a high- or a lowlevel input. When both signals are active, all eight outputs are enabled and the eight-bit addressed word can be read. When either signal is not active, all eight outputs are in a high-impedance state.

PRODUCTION DATA documents contain informat current as of publ

Copyright © 1985, Texas Instruments Incorporated

7-15

Pin 20 can be programmed during mask fabrication to be a chip-enable/power-down pin (E or E) or a secondary chip-select pin (\$\overline{S}2\) or \$S2). Each option can be active high or active low. When the chipenable/power-down pin is inactive, the chip is put into the standby mode. This reduces ICC1, which in the active state is 60 mA, to a standby ICC2 of 15 mA. With pin 20 programmed as a chip-select pin, it is functionally identical to pin 21.

#### data out (Q1-Q8)

The eight outputs must be enabled by pins 20 and 21 before the output word can be read. Data will remain valid until the address is changed or the outputs are disabled (chip deselected). When disabled, the threestate outputs are in a high-impedance state. Q1 is considered the least-significant bit, Q8 the most-significant

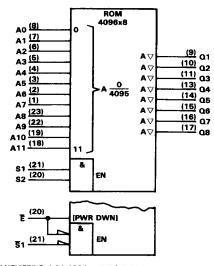

## logic symbol†

<sup>†</sup> This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12. Pins 20 and 21 can be active high as shown in the upper symbol or active low as shown in the lower (partial) symbol. In addition, pin 20 can be either a second chip-select (\$\overline{S}2\$ or \$2) or a chip-enable/power-down (\$\overline{E}\$ or \$E) pin.

## functional block diagram

## absolute maximum ratings

| Supply voltage range (see Note 1)    | 0.5 V to 7 V   |

|--------------------------------------|----------------|

| Output voltage range (see Note 1)    | 1 V to 7 V     |

| Input voltage range (see Note 1)     | 1 V to 7 V     |

| Power dissipation                    | 500 mW         |

| Operating free-air temperature range | 0°C to 70°C    |

| Storage temperature range            | -55°C to 150°C |

NOTE 1: Voltage values are with respect to VSS.

## recommended operating conditions

|     |                                | MIN | NOM | MAX    | UNIT |

|-----|--------------------------------|-----|-----|--------|------|

| Vcc | Supply voltage                 | 4.5 | 5   | 5.5    | ٧    |

| VIH | High-level input voltage       | 2   | ٧   | CC + 1 | ٧    |

| VIL | Low-level input voltage        | -1  |     | 0.8    | ٧    |

| TA  | Operating free-air temperature | 0   |     | - 70   | °C   |

# electrical characteristics, $T_A = 0$ °C to 70°C, $V_{CC} = 5$ V $\pm$ 10% (unless otherwise noted)

| PARAMETER |                                              | TEST CONDITIONS                    |                                                    |     | MAX | UNIT |

|-----------|----------------------------------------------|------------------------------------|----------------------------------------------------|-----|-----|------|

| VoH       | High-level output voltage                    | V <sub>CC</sub> = 4.5 V,           | I <sub>OH</sub> = -1 mA                            | 2.4 |     | V    |

| VOL       | Low-level output voltage                     | V <sub>CC</sub> = 4.5 V,           | I <sub>OL</sub> = 2.1 mA                           |     | 0.4 | V    |

| lj        | Input current                                | V <sub>CC</sub> = 5.5 V,           | 0 V ≤ V <sub>IN</sub> ≤ 5.5 V                      |     | 10  | μА   |

| lo        | Output leakage current                       | $V_0 = 0.4 \text{ V to V}_{CC}$    | Chip deselected                                    |     | ±10 | μА   |

| ICC1      | Supply current from V <sub>CC</sub> (active) | V <sub>CC</sub> = 5.5 V,           | V <sub>I</sub> = V <sub>CC</sub> output not loaded |     | 60  | mA   |

| ICC2      | Supply current from VCC (power down)         | V <sub>CC</sub> = 5.5 V            |                                                    |     | 15  | mA   |

| Ci        | Input capacitance                            | V <sub>O</sub> = 0 V,<br>f = 1 MHz | T <sub>A</sub> = 25°C,                             |     | 6   | pF   |

| co        | Output capacitance                           | V <sub>O</sub> = 0 V,<br>f = 1 MHz | $T_A = 25^{\circ}C,$                               |     | 12  | pF   |

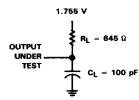

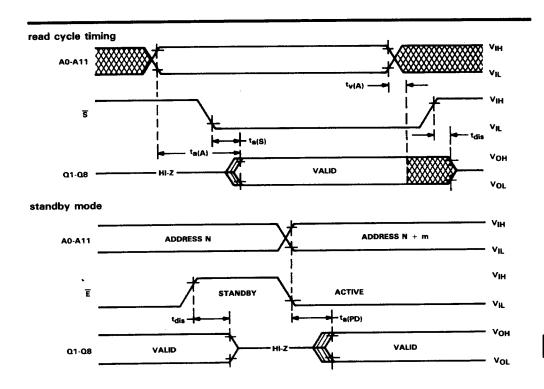

# switching characteristics, T<sub>A</sub> = $0^{\circ}$ C to $70^{\circ}$ C, V<sub>CC</sub> = $5 \text{ V} \pm 10\%$ (see Figure 1)<sup>†</sup>

|                    |                                                     |     | TMS4732-15 |     | TMS4732-20 |     | TMS4732-25 |      |

|--------------------|-----------------------------------------------------|-----|------------|-----|------------|-----|------------|------|

| PARAMETER          |                                                     | MIN | MAX        | MIN | MAX        | MIN | MAX        | UNIT |

| ta(A)              | Access time from address                            |     | 150        |     | 200        |     | 250        | ns   |

| ta(S)              | Access time from chip select                        |     | 120        |     | 120        |     | 120        | ns   |

| t <sub>a(PD)</sub> | Access time from chip enable/power down             |     | 150        |     | 200        |     | 250        | ns   |

| t <sub>V</sub> (A) | Output data valid after address change              | 0   |            | 0   |            | 0   |            | ns   |

| <sup>t</sup> dis   | Output disable time from chip select or chip enable |     | 100        |     | 100        |     | 100        | ns   |

<sup>†</sup> All AC measurements are made at 10% and 90% points.

# 7

#### PARAMETER MEASUREMENT INFORMATION

FIGURE 1. LOAD CIRCUIT

CODE ACQUISITION: The input media containing the customer programming data can be in the form of EPROMs, or data formatted in card images and transmitted via computer modem (contact TI for details on card image transmission). 32K EPROMS can be used to supply the customer data. In addition to the input media, the information requested in Table 1 is required at the same time in order to insure proper programming of device options and accurate data control.

#### TABLE 1. CUSTOMER/DEVICE INFORMATION

| CUSTOMER: SPECIFICATION NUMBER: ROM CODE NAME: ROM CODE CHECKSUM: |  |

|-------------------------------------------------------------------|--|

| 15 ALDHANI MEDIC CHADACTEDS DED LINE                              |  |

| ADDRESS ACCESS TIME (SPEED):                                      |  |

| PACKAGE TYPE: PLASTIC (N)                                         |  |

| PIN OPTIONS: 1 = HIGH, 0 = LOW, PD = POWER DOWN, CS = CHIP SELECT |  |

| PIN 20: PIN 21: PD/CS:                                            |  |

₹OMs