# Am9102/Am91L02 FAMILY

1024x1 Static R/W Random Access Memories

#### DISTINCTIVE CHARACTERISTICS

- Low-Power Dissipation

100 mW typical; 260 mW maximum

- Standby operating mode reduces power 84% 18 mW typical: 42 mW maximum

- Input and output voltage levels identical to TTL

- High-Output Drive Two full TTL loads guaranteed

- High Noise Immunity 400 mV guaranteed

- Uniform Access Times

Switching characteristics are insensitive to data patterns, addressing patterns, and power supply variations

- Single 5-Volt Power Supply

10% tolerance for full temperature range devices

5% tolerance for commercial range devices

- High-Performance Plug-In Replacement for: Intel 2102, Signetics 2602, Intersil IM7552, Mostek 4102, TI4033/4/5

- Available for operation over both commercial and military ranges

- 100% reliability assurance testing in accordance with MIL-STD-883

- Zero data hold and address hold times simplify timing requirements

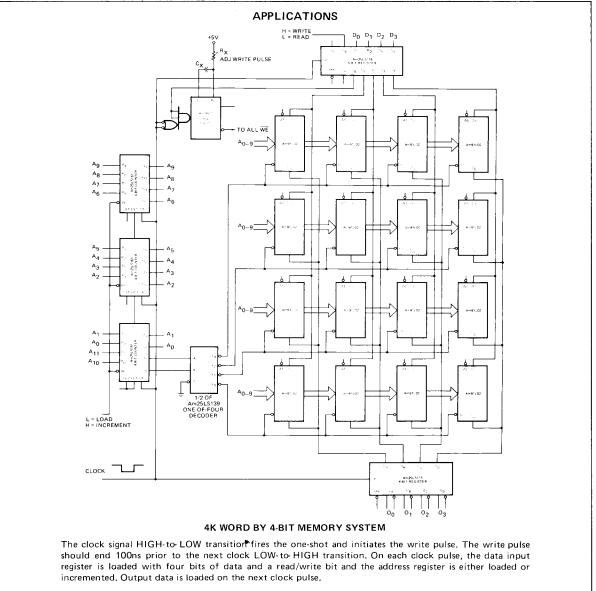

## **FUNCTIONAL DESCRIPTION**

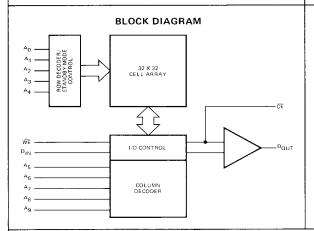

The Am9102 Family of 1024-bit static N-channel RAMs contains members with cycle times ranging from 650ns to 200ns. All the devices are organized as  $1024 \times 1$ , and all have a power-saving standby operating mode.

Each device has a chip enable input (CE) that controls a three-state output to make construction of large memory systems simple. Reading and writing are performed by enabling the chip and applying a LOW to write or a HIGH to read on the write enable input (WE). All inputs are directly TTL compatible with no external components required, and the output will drive two full TTL loads in both the HIGH and LOW states.

The devices operate from a single +5 volt power supply. The power dissipation of the devices can be reduced to about 16% of the normal operating power by lowering the voltage on the power supply pin. Data is guaranteed to be retained in the power-down condition.

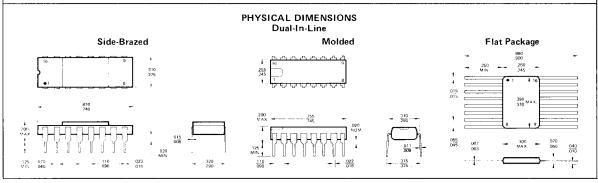

All unit members in the family are available in plastic or hermetic DIPs for operation over the commercial temperature range and, except for the Am9102D/E, may all also be purchased for operation over the military temperature range. All AC and DC parameters are guaranteed over the operating range.

# CONNECTION DIAGRAM Top View

Note: Pin 1 is marked for orientation.

## ORDERING INFORMATION

| AMBIENT<br>TEMPERATURE       | PACKAGE            | POWER<br>TYPE | ACCESS TIMES |            |            |            |            |           |  |  |  |

|------------------------------|--------------------|---------------|--------------|------------|------------|------------|------------|-----------|--|--|--|

|                              | TYPE               |               | 650ns        | 500ns      | 400ns      | 300ns      | 250ns      | 200ns     |  |  |  |

|                              | Molded DIP         | Standard      | AM9102PC     | AM9102APC  | AM9102BPC  | AM9102CPC  | AM9102DPC  | Am9102EPC |  |  |  |

| 0°C ≤ T <sub>A</sub> ≤ +70°C |                    | Low           | AM91L02PC    | AM91L02APC | AM91L02BPC | AM91L02CPC |            |           |  |  |  |

| A                            | Hermetic DIP       | Standard      | AM9102DC     | AM9102ADC  | AM9102BDC  | AM9102CDC  | AM9102DDC  | Am9102EDC |  |  |  |

|                              |                    | Low           | AM91L02DC    | AM91L02ADC | AM91L02BDC | AM91L02CDC | AM91L01CDC |           |  |  |  |

|                              |                    | Standard      | AM9102DM     | AM9102ADM  | AM9102BDM  | AM9102CDM  | AM9101CDM  |           |  |  |  |

| FE':0 110E' 0                | Hermetic DIP       | Low           | AM91L02DM    | AM91L02ADM | AM91L02BDM | AM91L02CDM | AM91L01CDM |           |  |  |  |

| -55°C to +125°C              | Hermetic Flat Pack | Standard      | AM9102FM     | AM9102AFM  | AM9102BFM  |            |            | _         |  |  |  |

|                              |                    | Low           | AM91L02FM    | AM91L02AFM | AM91L02BFM |            |            |           |  |  |  |

## MAXIMUM RATINGS above which the useful life may be impaired

| Storage Temperature                                          | -65°C to +150°C |

|--------------------------------------------------------------|-----------------|

| Ambient Temperature Under Bias                               | -55°C to +125°C |

| V <sub>CC</sub> With Respect to V <sub>SS</sub> , Continuous | -0.5 V to +7 V  |

| DC Voltage Applied to Outputs                                | -0.5 V to +7 V  |

| DC Input Voltage                                             | -0.5 V to +7 V  |

| Power Dissipation                                            | 1.0W            |

## **ELECTRICAL CHARACTERISTICS** over operating range

| m91L02PC,<br>m9102PC, A |                        | 0°C to +70°C                            | V <sub>CC</sub> = +5.0V ·5%        |         |      | 02/A/B<br>_02/A/B | Am9′<br>Am9′<br>Am9′ | 102D  |       |

|-------------------------|------------------------|-----------------------------------------|------------------------------------|---------|------|-------------------|----------------------|-------|-------|

| arameters               | Description            |                                         | Test Conditions                    |         | Min. | Max.              | Min.                 | Max.  | Units |

| <b>v</b> <sub>OH</sub>  | Output HIGH Voltage    | V <sub>CC</sub> = MIN., I <sub>OH</sub> | = -200µA                           |         | 2.4  |                   | 2.4                  |       | Volts |

| <b>v</b> <sub>OL</sub>  | Output LOW Voltage     | VCC = MIN., IOL                         | = 3.2mA                            |         |      | 0.4               |                      | 0.4   | Volts |

| VIH                     | Input HIGH Level       | Guaranteed input voltage for all input  |                                    | 2.0     | vcc  | 2.0               | vcc                  | Volts |       |

| VIL                     | Input LOW Level        | Guaranteed input voltage for all input  | -0.5                               | 0.8     | -0.5 | 0.8               | Volts                |       |       |

| ILI                     | Input Load Current     | V <sub>CC</sub> = MAX., V <sub>IN</sub> |                                    |         | 10   |                   | 10                   | μА    |       |

|                         |                        |                                         |                                    | Am91L02 |      | 28                |                      | 31    |       |

| ICC1                    |                        | All inputs = V <sub>CC</sub>            | T <sub>A</sub> = 25°C              | Am9102  |      | 45                |                      | 50    | 1     |

| Laca                    | Power Supply Current   | Data out open VCC = MAX.                | T <sub>A</sub> = 0°C               | Am91L02 |      | 30                |                      | 33    | mA    |

| ICC2                    |                        |                                         | Am910                              |         |      | 50                |                      | 55    |       |

| lo                      | 0.1-11-1-1-1           | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \   | V <sub>OUT</sub> = V <sub>CC</sub> |         |      | 5.0               |                      | 5.0   | ДА    |

|                         | Output Leakage Current | VCS = VIH                               | V <sub>OUT</sub> = 0.4V            |         | -10  |                   | -10                  | "     |       |

| m91L02DM<br>m9102DM, |                        | +125°C V <sub>C</sub>                           | C = +5.0V +10%                     |                         |      | 02/A/B<br>.02/A/B | Am9<br>Am91 | 102C<br>L02C |       |

|----------------------|------------------------|-------------------------------------------------|------------------------------------|-------------------------|------|-------------------|-------------|--------------|-------|

| rameters             | Description            |                                                 | Test Conditions                    |                         | Min. | Max.              | Min.        | Max.         | Unit  |

| V                    | Output HIGH Voltage    | IOH = -200µA                                    | V <sub>CC</sub> = 4.75V            | 2.4                     |      | 2.4               |             |              |       |

| V <sub>ОН</sub>      | Output HIGH Voltage    | 10Н200ДА                                        |                                    | V <sub>CC</sub> = 4.50V | 2.2  |                   | 2.2         |              | Volts |

| VOL                  | Output LOW Voltage     | V <sub>CC</sub> = MIN., I <sub>OL</sub> = 3.2mA |                                    |                         |      | 0.4               |             | 0.4          | Volts |

| VIH                  | Input HIGH Level       | Guaranteed input<br>voltage for all inpu        | 2.0                                | vcc                     | 2.0  | Vcc               | Volts       |              |       |

| VIL                  | Input LOW Level        | Guaranteed input<br>voltage for all inpu        | -0.5                               | 0.8                     | -0.5 | 0.8               | Volt        |              |       |

| ILI                  | Input Load Current     | V <sub>CC</sub> = MAX., V <sub>IN</sub>         | j = 0V to 5.5V                     |                         |      | 10                |             | 10           | μА    |

|                      |                        |                                                 | T 05°0                             | Am91L02                 |      | 28                |             | 31           |       |

| ICC1                 | D C                    | All inputs = V <sub>CC</sub>                    | T <sub>A</sub> = 25°C              | Am9102                  |      | 45                |             | 50           | 1     |

| lana                 | Power Supply Current   | V <sub>CC</sub> = MAX.                          | T 55°0                             | Am91L02                 |      | 35                |             | 37           | mA    |

| 1CC3                 |                        |                                                 | $T_A = -55^{\circ}C$               | Am9102                  |      | 55                |             | 60           |       |

| 1                    | Output Laskage Current | V== - V                                         | V <sub>OUT</sub> = V <sub>CC</sub> | - 1                     | 10   | 10                |             | 10           | μА    |

| LO                   | Output Leakage Current | VCS = VIH                                       | V <sub>OUT</sub> = 0.4V            |                         | _10  |                   | -10         | 1 "^         |       |

# **CAPACITANCE** $(T_A = 25^{\circ}C)$

| Parameters | Description                  | Test Conditions                   | Min. | Тур. | Max. | Units |

|------------|------------------------------|-----------------------------------|------|------|------|-------|

| CIN        | Input Capacitance, Any Input | V <sub>IN</sub> = 0 V, f = 1 MHz  | H    | 3.0  | 5.0  | pF    |

| COUT       | Output Capacitance           | V <sub>OUT</sub> = 0 V, f = 1 MHz |      | 4.0  | 6.0  | pF    |

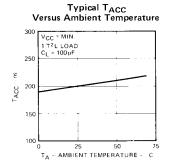

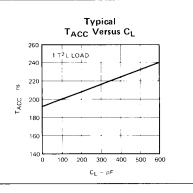

## Am9102 FAMILY SWITCHING CHARACTERISTICS AND OPERATING REQUIREMENTS

over operating temperature and voltage range

Load = 1 TTL gate and 100pF,  $V_{IL}$  = 0.8V,  $V_{IH}$  = 2.0V,  $t_r$  =  $t_f$  = 10ns. Output reference level 0.8V, 2.0V

|                            |                                                         |      | Am9102<br>Am91L02 |      |      |      | Am9102B<br>Am91L02B |      | Am9102C<br>Am91L02C |      | Am9102D |      | Am9102E |       |

|----------------------------|---------------------------------------------------------|------|-------------------|------|------|------|---------------------|------|---------------------|------|---------|------|---------|-------|

| Read Cycle Characteristics |                                                         | Min. | Max.              | Min. | Max. | Min. | Max.                | Min. | Max.                | Min. | Max.    | Min. | Max.    | Units |

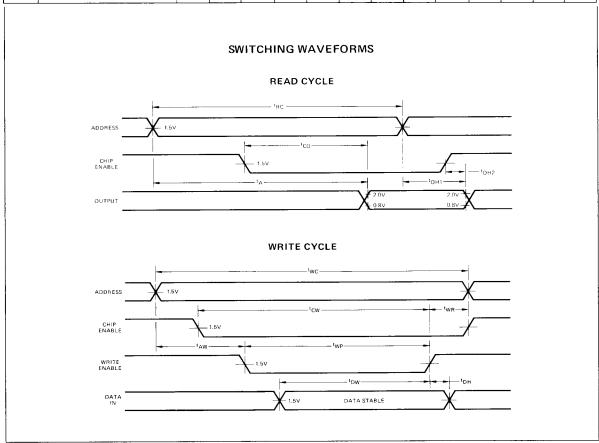

| <sup>t</sup> RC            | Read Cycle Time                                         | 650  |                   | 500  |      | 400  |                     | 300  |                     | 250  |         | 200  |         | ns    |

| tA                         | Access Time                                             |      | 650               |      | 500  |      | 400                 |      | 300                 |      | 250     |      | 200     | ns    |

| tCO                        | CE LOW to Output HIGH or LOW                            |      | 200               |      | 175  |      | 150                 |      | 125                 |      | 100     |      | 80      | ns    |

| tOH1                       | Previous Read Data Valid<br>with Respect to Chip Select | 50   |                   | 50   |      | 50   |                     | 50   |                     | 40   |         | 30   |         | ns    |

| †OH2                       | Previous Read Data Valid<br>with Respect to Chip Select | 0    |                   | 0    |      | 0    |                     | 0    |                     | 0    |         | 0    |         | ns    |

## Write Cycle Requirements

| tWC             | Write Cycle Time                           | 650 | 500 | 400 | 300 | 250 | 200 | ns |

|-----------------|--------------------------------------------|-----|-----|-----|-----|-----|-----|----|

| t <sub>AW</sub> | Address Set-Up Time                        | 20  | 20  | 20  | 20  | 20  | 20  | ns |

| twp             | Write Pulse Width                          | 200 | 175 | 150 | 125 | 100 | 80  | ns |

| twR             | Write Recovery Time<br>(Address Hold Time) | 0   | 0   | 0   | 0   | 0   | 0   | ns |

| t <sub>DW</sub> | Data Set-Up Time                           | 175 | 150 | 125 | 100 | 75  | 60  | ns |

| t <sub>DH</sub> | Data Hold Time                             | 0   | 0   | 0   | 0   | 0   | 0   | ns |

| tCW             | Chip Enable Set-Up Time                    | 200 | 175 | 150 | 125 | 100 | 85  | ns |

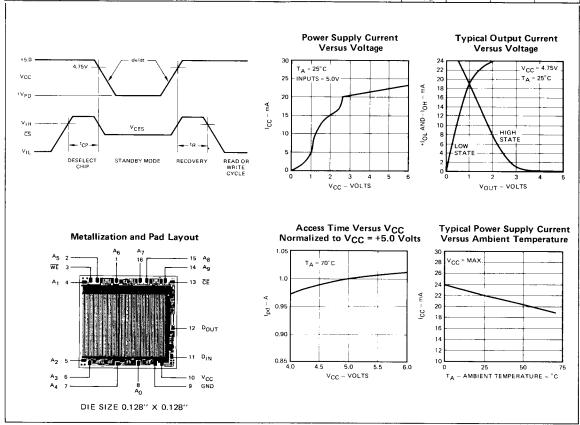

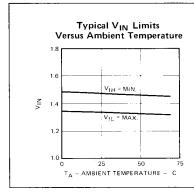

## POWER DOWN STANDBY OPERATION

The Am9102 Family is designed to maintain storage in a standby mode. The standby mode is entered by lowering  $V_{\rm CC}$  to around 1.5–2.0 volts (see table and graph below). When the voltage to the device is reduced, the storage cells are isolated from the data lines, so their contents will not change. The standby mode may be used by a battery operated backup power supply system, or, in a large system, memory pages not being accessed can be placed in standby to save power.

A standby recovery time must elapse following restoration of normal power before the memory may be accessed.

To ensure that the output of the device is in a high impedance OFF state during standby, the chip select should be raised for the chip disable time (t<sub>CP</sub>) prior to entering the standby mode, and should be held at V<sub>PD</sub> during the entire standby cycle.

## STANDBY OPERATING CONDITIONS OVER TEMPERATURE RANGE

| Parameters        | Description                       | Test                                          | Min.                                             | Тур.    | Max.            | Units |     |       |

|-------------------|-----------------------------------|-----------------------------------------------|--------------------------------------------------|---------|-----------------|-------|-----|-------|

| V <sub>PD</sub>   | V <sub>CC</sub> in Standby Mode   |                                               |                                                  |         | 1.5             |       |     | -     |

|                   |                                   |                                               | V <sub>PD</sub> = 1.5V                           | Am91L02 |                 | 10    | 23  |       |

|                   |                                   | TA = 0°C                                      | , TPD                                            | Am9102  |                 | 12    | 28  |       |

|                   |                                   | All Inputs = VpD                              | V <sub>PD</sub> = 2.0V                           | Am91L02 |                 | 12    | 28  | mA    |

| IPD               | I <sub>CC</sub> in Standby Mode   |                                               | 1,0                                              | Am9102  |                 | 15    | 38  |       |

|                   |                                   |                                               | V <sub>PD</sub> = 1.5V<br>V <sub>PD</sub> = 2.0V | Am91L02 |                 | 10    | 26  |       |

|                   |                                   | $T_A = -55^{\circ}C$<br>All Inputs = $V_{PD}$ |                                                  | Am9102  |                 | 12    | 31  |       |

|                   |                                   |                                               |                                                  | Am91L02 |                 | 12    | 31  | mA    |

|                   |                                   |                                               |                                                  | Am9102  |                 | 15    | 42  |       |

| dv/ <sub>dt</sub> | Rate of Change of V <sub>CC</sub> |                                               |                                                  |         |                 |       | 1.0 | V/µs  |

| <sup>t</sup> R    | Standby Recovery Time             |                                               |                                                  |         | TRC             |       |     | ns    |

| ТСР               | Chip Deselect Time                |                                               |                                                  |         | 0               |       |     | ns    |

| V <sub>CES</sub>  | CE Bias in Standby                |                                               |                                                  |         | V <sub>PD</sub> |       |     | Volts |

Copyright (c) 1988-93 Reed Publishing (USA) Inc. ALL RIGHTS RESERVED.

THIS IMAGE DATABASE HAS BEEN CREATED BY CAHNERS TECHNICAL INFORMATION SERVICE, A DIVISION OF REED PUBLISHING (USA)., AND IS PROPRIETARY TO CAHNERS TECHNICAL INFORMATION SERVICE. NO PART OF THIS DATABASE MAY BE PUPLICATED IN HARD COPY OR MACHINE READABLE FORM WITHOUT PRIOR WRITTEN AUTHORIZATION FROM CAHNERS TECHNICAL INFORMATION SERVICE, EXCEPT THAT LICENSEE IS GRANTED A LIMITED, NON-EXCLUSIVE LICENSE TO REPRODUCE LIMITED PORTIONS OF THE DATABASE FOR LICENSEE'S INTERNAL USE PROVIDED THAT A SUITABLE NOTICE OF COPYRIGHT IS INCLUDED ON ALL COPIES. UNDER NO CIRCUMSTANCES MAY COPIES BE MADE FOR RESALE IN ANY MEDIA.

## **DEFINITION OF TERMS**

#### **FUNCTIONAL TERMS**

$\overline{CE}$  Active LOW chip enable. Data can be read from or written into the memory only if  $\overline{CE}$  is LOW.

$\overline{\text{WE}}$  Active LOW write enable. Data is written into the memory if  $\overline{\text{WE}}$  is LOW and read from the memory if  $\overline{\text{WE}}$  is HIGH.

**Static RAM** A random access memory in which data is stored in bistable latch circuits. A static memory will store data as long as power is supplied to the chip without requiring any special clocking or refreshing operations.

N-Channel An insulated gate field effect transistor technology in which the transistor source and drains are made of N-type material, and electrons serve as the carriers between the two regions. N-Channel transistors exhibit lower thresholds and faster switching speeds than P-Channel transistors.

#### SWITCHING TERMS

t<sub>RC</sub> Read Cycle Time. The minimum time required between successive address changes while reading.

$\mathbf{t}_{A}$  Access Time. The time delay between application of an address and stable data on the output when the chip is enabled.

t<sub>CO</sub> Access Time from Chip Enable, The minimum time during

which the chip enable must be LOW prior to reading data on the output.

tOH1 Minimum Access Time, Minimum time which will elapse between change of address and any change on the data output.

$t_{\mbox{OH2}}$  Minimum time which will elapse between a change on the chip enable and any change on the data output.

$t_{WC}$  Write Cycle Time. The minimum time required between successive address changes while writing.

$t_{\rm AW}$  Address Set-Up Time. The minimum time prior to the falling edge of the write enable during which the address inputs must be correct and stable.

$t_{WP}$  The minimum duration of a LOW level on the write enable guaranteed to write data.

$t_{WR}$  Address Hold Time. The minimum time after the rising edge of the write enable during which the address must remain steady.

$t_{\mbox{\scriptsize DW}}$  Data Set-Up Time. The minimum time that the data input must be steady prior to the rising edge of the write enable.

$t_{

m DH}$  Data Hold Time. The minimum time that the data input must remain steady after the rising edge of the write enable.

$t_{CW}$  Chip Enable Time During Write. The minimum duration of a LOW level on the Chip Select while the write enable is LOW to quarantee writing.