## 7224 CONTROLLER FOR 4MBIT BPK 5V74 BUBBLE MEMORY SUBSYSTEM

- Provides Interface between Host Microprocessor and 4 Mbit Bubble Memory Subsystems

- Interfaces to 8080/85/86/88/186/286 and Other Standard Microprocessors

- Controls up to Eight Bubble Memory Subsystems

- 18 Easy-to-Use Commands

- Three Modes of Data Transfer

- DMA

- Polled

- Interrupt

- Transfer of Single (64 bytes) or Multiple Pages of Data

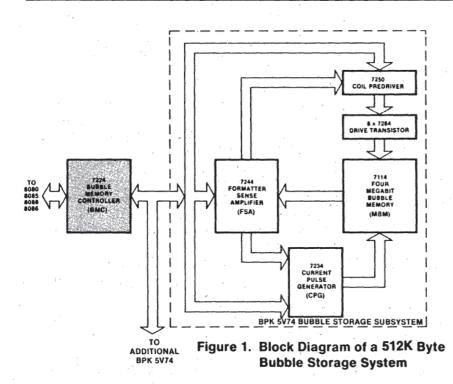

The 7224 is a complete 4 Mbit Bubble Memory Controller (BMC) that provides the interface between the microprocessor host and the 4 Mbit Bubble Memory Subsystem. All communication between the host processor and the bubble memory is performed through the controller.

The BMC interfaces easily to any Intel microprocessor or other standard microprocessor. The user has 18 easy-to-use commands available. Information such as the starting page location, the number of pages to be transferred and a read or write command is passed to the BMC before the read or write operation is initiated.

The 18 commands of the 4Mbit BMC is a superset of the 1Mbit BMC's 16 commands providing an easy up-grade of software from the 1Mbit to the 4Mbit system.

The design engineer writes a bubble memory software driver to integrate the bubble memory into his system. This interfacing with the BMC is similar to interfacing a disk drive controller. Application notes and manuals describe the details of interfacing to the BMC.

The BMC can transfer data in DMA, interrupt or polled mode. Data is transferred in and out of the bubble memory subsystem via the controller in single or multiple pages. A page size may vary from 64 bytes in a single bubble system and up to 512 bytes in an eight bubble system.

Figure 2.

Pin Configuration

The BMC has an eight bit data bus plus parity bit. Word length expansion to 16 bit is possible by operating two controllers in parallel.

The BMC generates all the timing and control signals to the BPK 5V74 subsystem.

One BMC can control up to eight BPK 5V74 subsystems. This provides an easy expansion path to expand any 4 Mbit (512K byte) system up to 32Mbit (4Mbyte) by adding on additional BPK 5V74 subsystems.

The BMC is manufactured using Intel's high performance HMOS process and is packaged in a standard 40-pin dual-in-line package. All inputs are directly TTL compatible and the device uses a single +5 Volt supply.

#### HARDWARE DESCRIPTION

The 7224 Bubble Memory Controller is packaged in a 40-pin Dual In-Line Package (DIP). The following lists the individual pins and describes their function.

Table 1. Pin Description

| Signal Name                    | Pin No. | 1/0 | Source/Destination                                    | Description                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------------------------|---------|-----|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>CC</sub>                | 40      | -   |                                                       | +5 VDC Supply                                                                                                                                                                                                                                                                                                                                                                                   |

| GND                            | 20      | 1   |                                                       | Ground                                                                                                                                                                                                                                                                                                                                                                                          |

| PWR.FAIL 1 · I                 |         |     | 7234 CPG                                              | A low forces a controlled stop sequence and holds BMC in an IDLE state (similar to RESET).                                                                                                                                                                                                                                                                                                      |

| RESET.OUT                      | 2       | 0   | 7250 CPD/7244 FSA<br>7234 Reference<br>Current Switch | An active low signal to disable external logic initiated by PWR.FAIL or RESET signals, but not active until a stopping point in a field rotation is reached (if the BMC is causing the bubble memory drive field to be rotated).                                                                                                                                                                |

| CLK                            | 3       |     | Host Bus                                              | 2 MHz, TTL-level clock.                                                                                                                                                                                                                                                                                                                                                                         |

| RESET                          | 4       | 1   | Host Bus                                              | A low on this pin forces the interruption of any BMC sequencer activity, performs a controlled shut-down, and initiates a reset sequence. After the reset sequence is concluded, a low on this pin causes a low on the RESET.OUT pin, furthermore, the next BMC sequencer command must be either the Initialize or Abort command; all other commands are ignored.                               |

| RD                             | 5       | 1   | Host Bus                                              | A low on this pin enables the BMC output data to be transferred to the host data bus (D <sub>0</sub> -D <sub>8</sub> ).                                                                                                                                                                                                                                                                         |

| WR                             | 6       | 1   | Host Bus                                              | A low on this pin enables the contents of the host data bus (D <sub>0</sub> -D <sub>8</sub> ) to be transferred to the BMC.                                                                                                                                                                                                                                                                     |

| DACK                           | 7       |     | Host Bus                                              | A low signal is a DMA acknowledge. This notifies the BMC that the next memory cycle is available to transfer data. This line should be active only when DMA transfer is desired and the DMA ENABLE bit has been set. $\overline{CS}$ should not be active during DMA transfers except to read status. If DMA is not used, $\overline{DACK}$ requires an external pullup to $V_{CC}$ (5.1K ohm). |

| DRQ                            | 8       | 0   | Host Bus                                              | A high on this pin indicates that a data transfer between the BMC and the host memory is being requested.                                                                                                                                                                                                                                                                                       |

| INT                            | 9       | 0   | Host Bus                                              | A high on this pin indicates that the BMC has a new status and requires servicing when enabled by the host CPU.                                                                                                                                                                                                                                                                                 |

| A <sub>0</sub>                 | 10      | 1   | Host Bus                                              | A high on this pin selects the command/status registers. A low on this pin selects the data register.                                                                                                                                                                                                                                                                                           |

| D <sub>0</sub> -D <sub>7</sub> | 11-18   | I/O | Host Bus                                              | Host CPU data bus. An eight-bit bidirectional port which can be read or written by using the RD and WR strobes. D <sub>0</sub> shall be the LSB.                                                                                                                                                                                                                                                |

|                                |         |     |                                                       |                                                                                                                                                                                                                                                                                                                                                                                                 |

Table 1. Pin Description (Continued)

| Signal Name                                           | Pin No. | 1/0 | Source/Destination                                                                     | Description                                                                                                                                                                                                                                                                                                                                               |

|-------------------------------------------------------|---------|-----|----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CS                                                    | 21      | _   | Host Bus                                                                               | Chip Select Input. A high on this pin shall disable the device to all but DMA transfers (i.e., it ignores bus activity and goes into a high impedance state).                                                                                                                                                                                             |

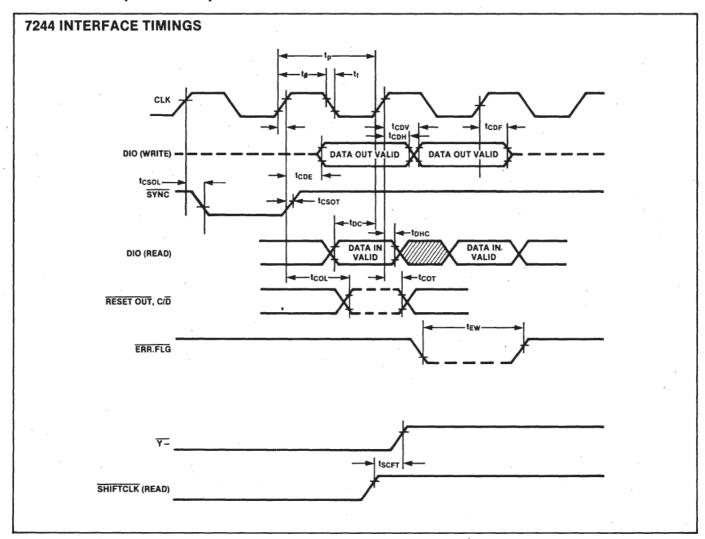

| DIO                                                   | 22      | I/O | 7244 FSA                                                                               | A bidirectional active high data line that shall be used for serial communications with 7244 FSA devices.                                                                                                                                                                                                                                                 |

| SYNC                                                  | 23      | 0   | 7244 FSA                                                                               | An active low output utilized to create time division multiplexing slots in a 7244 FSA chain. It shall also indicate the beginning of a data or command transfer between BMC and 7244 FSA.                                                                                                                                                                |

| SHIFT.CLK                                             | 24      | 0   | 7244 FSA                                                                               | A controller generated clock that initiates data transfer between selected FSAs and their corresponding bubble memory devices. The timing of SHIFT.CLK shall vary depending upon whether data is being read or written to the bubble memory.                                                                                                              |

| BUS.RD                                                | 25      | 0   | To User External<br>Circuit                                                            | An active low signal that indicates that the DIO line is in the output mode, i.e., BMC is sending data to FSA. It shall be used to allow off-board expansion of 7244 FSA devices.                                                                                                                                                                         |

| WAIT                                                  | 26      | I/O | To Alternate<br>Controller(s)<br>When User System<br>Uses More Than<br>One Controller. | A bidirectional pin that shall be tied to the WAIT pin on other BMCs when operated in parallel. It shall indicate that an interrupt has been generated and that the other BMCs should halt in synchronization with the interrupting BMC. WAIT is an open collector active low signal. Requires an external pullup resistor to V <sub>cc</sub> (5.1K ohm). |

| ERR.FLG                                               | 27      | 1   | 7244 FSA                                                                               | An active low input generated externally by 7244 FSA indicating that an error condition exists. It is an open collector input which requires an external pullup resistor (5.1K ohm).                                                                                                                                                                      |

| DET.ON                                                | 28      | 0   | To User External<br>Circuit                                                            | An active low signal that indicates the system is in the read mode and may be detecting. It is useful for power saving in the MBM.                                                                                                                                                                                                                        |

| C/D                                                   | 29      | 0   | 7244 FSA                                                                               | A high on this line indicates that the BMC is beginning an FSA command sequence. A low on this line indicates that the BMC is beginning a data transmit or receive sequence.                                                                                                                                                                              |

| BOOT.SW.EN                                            | 30      | 0   | 7234 CPG                                                                               | An active low signal which may be used for enabling the BOOT.SWAP of the 7234 CPG.                                                                                                                                                                                                                                                                        |

| SWAP.EN                                               | 31      | 0   | 7234 CPG                                                                               | An active low signal used to create the swap function in external circuits.                                                                                                                                                                                                                                                                               |

| BOOT.EN                                               | 32      | 0   | 7234 CPG                                                                               | An active low signal enabling the bootstrap loop replicate function in external circuitry.                                                                                                                                                                                                                                                                |

| REP.EN                                                | 33      | 0   | 7234 CPG                                                                               | An active low signal used to enable the replicate function in external circuitry.                                                                                                                                                                                                                                                                         |

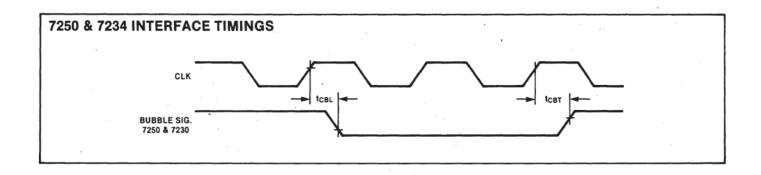

| TM.B                                                  | 34      | 0   | 7234 CPG                                                                               | An active low timing signal generated by the decoder logic for determining TRANSFER pulse width.                                                                                                                                                                                                                                                          |

| TM.A                                                  | 35      | 0   | 7234 CPG                                                                               | An active low timing signal generated by the decoder logic for determining CUT pulse width.                                                                                                                                                                                                                                                               |

| $\frac{\overline{Y}-}{X-}, \frac{\overline{Y}+}{X+},$ | 36-39   | 0   | 7250 CPD                                                                               | Four active low timing signals generated by the decoding logic and used to create coil drive currents in the bubble memory device.                                                                                                                                                                                                                        |

#### **FUNCTIONAL DESCRIPTION**

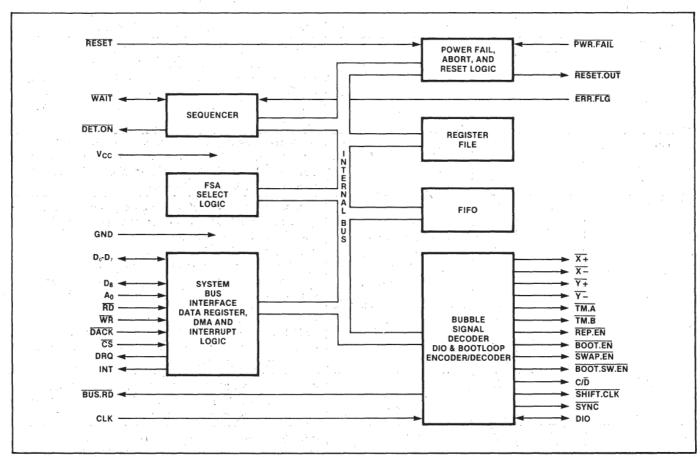

The 7224 Bubble Memory Controller provides the user interface to the bubble memory system. The BMC generates all memory system timing and control, maintains memory address information, interprets and executes user request for data transfers, and provides a

Microprocessor-Bus compatible interface for the magnetic bubble memory system.

Figure 3 is a block diagram of the 7224 Bubble Memory Controller (BMC). The following paragraphs describe the functions of the individual functional sections of the BMC.

Figure 3. 7224 Bubble Memory Controller (BMC), Block Diagram

System Bus Interface—The System Bus Interface (SBI) logic contains the timing and control logic required to interface the BMC to a non-multiplexed bus. The logic also contains the circuitry to check and generate odd parity on transfers across the bus. The interface has input data, output data, and status data latches. The BMC can interface asynchronously to the host CPU. With a 2-MHz clock, it is capable of sustaining a 1 Mbyte per second transfer rate while data is available in the BMC FIFO.

FIFO—The FIFO consists of a 40 x 8 bit FIFO RAM for data storage. The FIFO block also contains input and output data latches, providing double data buffering, to improve the R/W cycle times seen at the system bus interface. The FIFO may be used as a general purpose FIFO when a command is not being executed by the BMC Sequencer. In this mode, the FIFO READY status bit becomes a FIFO not-empty indicator indicating that

the RAM and input/output latches have at least one byte of data.

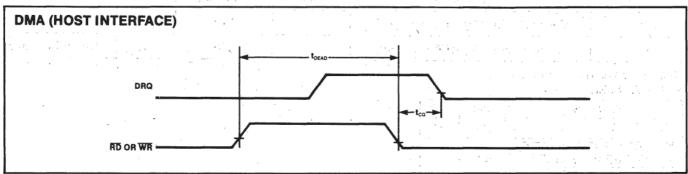

**DMA and Interrupt Logic**—The DRQ pin has two functions:

- (1) If the DMA enable bit in the enable register is set, the DRQ pin, in conjunction with the DACK pin, provides a standard DMA transfer capability; i.e., it has the ability to handshake with an 8257 or 9517/8237 DMA controller chip.

- (2) If the DMA enable bit is reset, the DRQ pin acts as a "ready for data transfer interrupt" pin. It becomes active when 22 bytes may be read from or written into the BMC; it is reset when this condition no longer exists.

Register File— The register file contains 6 eight-bit registers that are accessible by the host CPU. Refer to the Register Section for details.

MBM Address Logic and RAM—The MBM address logic consists of the block length counter, starting address counter, adder, and MBM Address RAM. The MBM Address RAM is used to store the next available page address for each of up to 8 dual FSAs. The address maintained is the read address; the write address is generated, when needed, by adding a constant to the stored read address.

The block length counter enables multiple page transfers of up to 2048 pages in length.

The starting address counter is used as a register to hold the desired start address. Once the start address is reached, the counter is incremented on each subsequent page transfer so that its value equal to the present read address. There are 8192 possible starting addresses.

DIO Bootloop Decoder/Encoder — Performs parallel-to-serial and serial-to-parallel conversions between the FIFO data and the serial bit stream on the DIO line. This block also generates the BUS.RD signal, which indicates the direction of data transfer on the DIO line (this is useful in situations which require external buffering on the DIO line). This block also contains the circuitry which decodes the bootloop data during a Read Bootloop or Initialize operation, and encodes the bootloop data during a Write Bootloop operation.

Sequencer—Controls the execution of commands by decoding the contents of its own internal ROM in which the BMC firmware is located. This block also sets and resets flags and status bits, and controls actions in other parts of the BMC.

Power Fail and Reset—Provides a means of resetting the bubble systems in an orderly manner, when activated by the PWR.FAIL signal, the RESET signal, or the ABORT command. The additive noise on the PWR.FAIL pin should be less than 150 mV for proper powerfail operation.

FSA Select Logic block contains the logic which controls the timing of the interaction between the BMC and the FSAs. The FSA selection is determined by the four high-order bits in the BLR and the three high-order bits in the AR, both set by the user.

**Bubble Signal Decoder** block contains the logic for creating all the MBM timing signals. The BMC to bubble memory interface consists of active low timing signals. The starting and stopping point of each signal is determined by the decoder logic. Each signal may occur every field rotation or only once in a number of field rotations. The field rotation in which a timing pulse occurs is controlled by the sequencer logic.

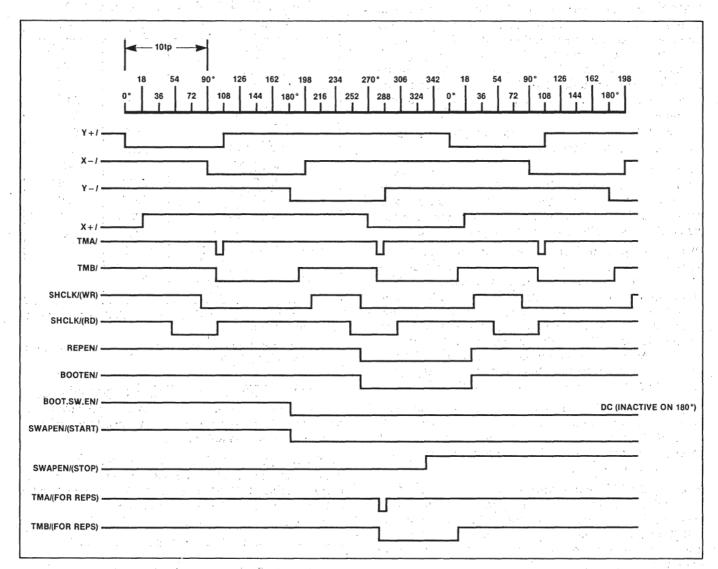

Figure 4 and Table 2 illustrate the typical timing signals for the BMC. These signals are described in the following paragraphs.

$\overline{X}+$ ,  $\overline{X}-$ ,  $\overline{Y}+$ , and  $\overline{Y}-$  go to the 7250 CPDs, and are used to enable the coil drive currents in the MBMs.

TM.A and TM.B go to the 7234 CPGs, and are used to determine, respectively, the pulse widths for the CUT and TRANSFER functions used in replicating and generating the bubbles.

Table 2. 7224 BMC Timing (Degrees)\*\*

| Signal                      | Start           | Width        |

|-----------------------------|-----------------|--------------|

| X±                          | 270°            | 108°         |

| <u>Y+</u>                   | 0°              | 108°         |

| <del>x-</del>               | 90°             | 108°         |

| <u>∀</u> −                  | 180°            | 108°         |

| TM.A (LATE)                 | 279°            | 94.5°        |

| TM.A (EARLY)                | 99°             | 94.5°        |

| TM.B (LATE)                 | 279°            | 90°          |

| TM.B (EARLY)                | 99°             | 90°          |

| BOOT.EN                     | 261°            | 126°         |

| REP.EN                      | 261°            | 126°         |

| SWAP.EN                     | 180°            | 153°         |

| BOOT.SW.EN                  | 180°            | DC*          |

| SHIFTCLK (RD) LATE<br>EARLY | 230.5°<br>40.5° | 45°<br>63°   |

| SHIFTCLK (WR) LATE<br>EARLY | 261°<br>81°     | 126°<br>126° |

<sup>\*</sup>Stays low for 8211 field rotation periods when writing the MBM Bootloop.

SWAP.EN, REP.EN, BOOT.SW.EN, and BOOT.EN all go to the 7234 CPG. They are used to enable, respectively, the data swap, data replicate, boot swap, and boot replicate functions within the MBMs.

SHIFT.CLK goes to the FSAs. It is used to control the timing of events at the interface between each FSA and its corresponding MBM. (Refer to 7244 FSA Specification for a description of the BMC/FSA interface.)

$\overline{\text{SYNC}}$  and  $\overline{\text{C/D}}$  control the serial communications between the BMC and the FSAs (on the DIO line).

#### **USER-ACCESSIBLE REGISTERS**

The user operates the bubble memory system by reading from or writing to specific registers within the bubble memory controller (BMC). The following paragraphs identify these registers and gives brief functional descriptions, including bit configurations and address assignments.

#### Register Addressing

Selection of the user-accessible registers depends on register address information sent from the user to the BMC. This address information is sent via a single address line (designated  $A_0$ ) and data bus lines  $D_0$  through  $D_5$ .

The Command Register (CMDR) is an 8-bit register which is loaded from  $D_0 - D_7$ . Register Address Counter (RAC) is a 4-bit register which is loaded from  $D_0 - D_3$ . The status register is selected and read by a single read request. The command register is selected and loaded by a single write request. The remaining registers are accessed indirectly, and the desired register is first selected by placing its address in the RAC, and then read or written with a subsequent read or write request.

<sup>\*\*</sup>All phases relative to Y + start phase. All entries  $\pm$  1.26 except TM.A width which is  $\pm$  0.5.

Figure 4. 7224 BMC Timing Diagram

Table 3 gives a complete listing of the address asignments for the user-accessible registers. The registers are listed in two groups. The first group (STR, CMDR, RAC) consists of those registers that are selected and accessed in one operation. The second group (UR, BLR, ER, AR, FIFO) consists of those registers that are addressed indirectly by the contents of RAC.

Table 3. Address Assignments for the User-Accessible Registers

|                            | ,      | _                           |            |

|----------------------------|--------|-----------------------------|------------|

| A0 D7 D6 D5 D4 D3 D2 D1 D0 | Symbol | Name of Register            | Read/Write |

| 1 0 0 C 1 C C C            | CMDR   | Command<br>Register         | Write Only |

| 1 0 0 M 0 B B B B          | RAC    | Register Address<br>Counter | Write Only |

| 1 S S S S S, S S S.        | STR    | Status Register             | Read Only  |

Table 3. Address Assignments for the User-Accessible Registers (Continued)

| A0 | В3 | RAC<br>B2 | _ | во | Symbol  | Name of Register             | Read/Write    |

|----|----|-----------|---|----|---------|------------------------------|---------------|

| 0  | 1  | 0         | 1 | 1  | BLR LSB | Block Length<br>Register LSB | Write Only    |

| 0  | 1  | 1         | 0 | 0  | BLR MSB | Block Length<br>Register MSB | Write Only    |

| 0  | 1  | 1         | 0 | 1. | ER      | Enable Register              | Read or Write |

| 0  | 1, | 1         | 1 | 0  | AR LSB  | Address Register<br>LSB      | Read or Write |

| 0  | 1  | 1         | 1 | 1  | AR MSB  | Address Register<br>MSB      | Read or Write |

| Ó  | 0  | 0         | Ó | 0  | FIFO    | FIFO Data Buffer             | Read or Write |

SSSSSSS = 8-bit status information returned to the user from the STR

CCCCC = 5-bit command code sent to the CMDR by the user.

BBBB = 4-bit register address sent to the RAC by the user.

B3B2B1B0 = 4-bit contents of RAC at the time the user makes a read or write request with A0 = 0.

LSB = Least Significant Byte

MSB = Most Significant Byte

M = Modifier (When written high will clear any pending interrupt from 7224 without destroying any data present in the FIFO and its associated latches.

The register file contains the registers with address 1011 through 1111. These registers are also called parametric registers because they contain flags and parameters that determine exactly how the BMC will respond to commands written to the CMDR.

To facilitate such operations, the BMC automatically increments the RAC by one count after each transfer of data to or from a parametric register.

The RAC increments from the initially loaded value through address 1111 and then on to 0000 (the FIFO address). When it has reached 0000, it no longer increments. All subsequent data transfers (with A0 = 0) will be to or from the FIFO until such time as the RAC is loaded with a different register address.

#### **REGISTER DESCRIPTIONS**

### Command Register (CMDR) 4 Bits, Write Only

The user issues a command to the BMC by writing a 5-bit command code to the CMDR.

Table 4 lists the 5-bit command codes used to issue the eighteen commands recognized by the BMC.

Table 7 is a listing of the commands and their functions.

**Table 4. Command Code Definitions**

| D5 | D3  | D2  | D1 | Do     | Command Name                   |  |  |

|----|-----|-----|----|--------|--------------------------------|--|--|

| 1  | 0   | 0   | 0  | 0      | Write Bootloop Register Masked |  |  |

| 0  | 0   | 0   | 0  | 1      | Initialize                     |  |  |

| 0  | 0   | 0   | 1  | 0      | Read Bubble Data               |  |  |

| 0  | 0   | 0   | 1  | 1-1    | Write Bubble Data              |  |  |

| 0  | 0   | 1   | 0  | 0      | Read Seek                      |  |  |

| 0  | 0   | 11, | 0  | 1      | Read Bootloop Register         |  |  |

| 0  | 0   | -1  | 1  | 0      | Write Bootloop Register        |  |  |

| 0  | 0   | 1   | 1  | . 1    | Write Bootloop                 |  |  |

| 0  | :1  | 0   | 0  | 0      | Read FSA Status                |  |  |

| 0  | 1   | 0   | 0  | 1.     | Abort                          |  |  |

| 0  | 1   | 0   | 1  | 0      | Write Seek                     |  |  |

| 0  | 1   | 0.  | 1  | 1 -    | Read Bootloop                  |  |  |

| 0  | . 1 | 1   | 0  | 0      | Read Corrected Data            |  |  |

| 0  | 1   | 1   | 0  | . 1, . | Reset FIFO                     |  |  |

| 0  | 1   | 1   | 1  | 0      | MBM Purge                      |  |  |

| 0. | 1   | 1   | .1 | 1      | Software Reset                 |  |  |

| 1  | 0   | . 0 | 0  | 1      | Zero Access Read Seek          |  |  |

| 1  | 0   | 0   | 1  | 0      | Zero Access Read Bubble Data   |  |  |

The most commonly used commands in normal operation are:

Initialize

Read Bubble Data

Write Bubble Data

Reset FIFO

Read Seek

Write Seek

Abort

Read Corrected Data

Software Reset

Read FSA Status

MBM Purge

Zero Access Read Seek Zero Access Read Bubble Data Commands relating to the bootloop, and used only for diagnostic purposes, are:

Read Bootloop Register Write Bootloop Register Write Bootloop Register Masked Read Bootloop Write Bootloop

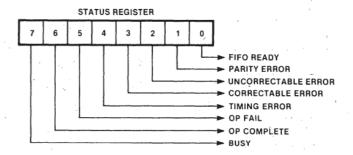

#### Status Register (STR) 8 Bits, Read Only

The user reads the BMC status register in response to an interrupt signal, or as part of the polling process in a polled data transfer mode. The status register provides information about error conditions, completion or termination of commands, and about the BMC's readiness to transfer data or accept new commands. The individual bit descriptions are as follows:

BUSY (when = 1) indicates that the BMC is in the process of executing a command. When equal to 0, BUSY indicates that the BMC is ready to receive a new command.

OP COMPLETE (when = 1) indicates the successful completion of a command.

OP FAIL (when = 1) indicates that the BUSY bit has gone inactive with either the TIMING ERROR or UNCORRECTABLE ERROR bits active.

TIMING ERROR (when = 1) indicates that a FSA has reported a timing error to the BMC, or that the host system has failed to keep up with the BMC, thereby causing the BMC FIFO to overflow or to underflow. TIMING ERROR is also set if no bootloop sync word is found during initialization, or if a Write Bootloop command is issued when the WRITE BOOTLOOP ENABLE bit is equal to zero in the enable register, or the Write Bootloop Register Masked command is sent without an adequate number of 1's present in data pattern.

CORRECTABLE ERROR (when = 1) indicates that a FSA has reported to the BMC that a correctable error has been detected in the last data block transferred.

UNCORRECTABLE ERROR (when = 1) indicates that at least one FSA has reported to the BMC that an uncorrectable error has been detected in the last data block transferred.

PARITY ERROR (when = 1) indicates that the BMC's parity check circuitry has detected a parity error on a data byte sent to the BMC by the user on the data lines  $D_0$ - $D_8$ .

FIFO READY has two functions. The FIFO READY functions are as follows:

NOTE: IF RAC # FIFO, FIFO READY = 1

| STATUS B   | ITS    | READ                               | WRITE            |  |

|------------|--------|------------------------------------|------------------|--|

| FIFO READY | BUSY   | MEAD                               |                  |  |

| 1          | 1      | data in<br>FIFO                    | space in<br>FIFO |  |

| 0          | 1      | no data                            | no space         |  |

| 1<br>0     | 0<br>0 | — data in FIFO —<br>— FIFO empty — |                  |  |

Although the status word can be read at any time, the status information, bit 1 through 6, is not valid until the BUSY bit is low.

STR Bits 1 through 6 are reset when a new command is issued. They may also be reset by making a write request (WR=0) to the BMC with  $A_0$ =1,  $D_4$ =0, and  $D_5$ =1 (Modified bit) (that is, writing the RAC with  $D_5$ =1). This operation also resets the "INT" pin to "0". NOTE: A byte of FIFO data can be lost when using this procedure if the RAC is written to other than the FIFO address when data is still present in FIFO.

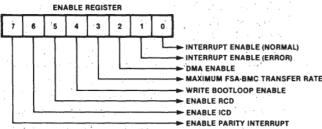

#### Enable Register (ER) 8 Bits, Write Only

The user sets various bits of the enable register to enable or disable various functions within the BMC or the FSAs. The individual bit descriptions are as follows:

In the above figure and in the text below, the following abbreviations are used:

ICD = INTERNALLY CORRECT DATA

RCD = READ CORRECTED DATA

UCE = UNCORRECTABLE ERROR

CE = CORRECTABLE ERROR

TE = TIMING ERROR

ENABLE PARITY INTERRUPT enables the BMC to interrupt the host system (via the INT line) when the BMC detects a parity error on the data bus lines  $D_0$ - $D_7$ .

ENABLE ICD enables the BMC to give the Internally Correct Data command to the FSAs when an error has been detected by the FSA's error detection and correction circuitry. Each FSA responds to such a command by internally cycling the data through its error correction network. When finished, the FSA returns status to the BMC as to whether or not the error is correctable. The value of ENABLE ICD affects the action of INTERRUPT ENABLE (ERROR).

ENABLE RCD enables the BMC to give the Read Corrected Data command to the FSAs when an error has been detected. This causes each FSA to correct the error (if possible) and also to transfer the corrected data to the BMC. The Read Corrected Data command is also used to read into the BMC data previously corrected by the FSA in response to an Internally Correct Data command. In either case, when the data transfer has been completed, the BMC reads each FSA's status to determine whether or not the error was correctable. In the case of an uncorrectable error, bad data may have been sent to the user. The value of ENABLE RCD affects the action of INTERRUPT ENABLE (ERROR).

WRITE BOOTLOOP ENABLE (when = 1) enables the bootloop to be written. If this bit is equal to zero, and a Write Bootloop command is received by the BMC, the command is aborted and the TIM-ING ERROR bit is set in the STR.

DMA ENABLE (when = 1) enables the BMC to operate in DMA data transfer mode, using the DRQ and DACK signals in interaction with a DMA controller. When equal to zero, DMA ENABLE sets up the controller to support interrupt driven or polled data transfer.

INTERRUPT ENABLE (ERROR) selects error conditions under which the BMC stops command execution and interrupts the host processor (via the INT line). INTERRUPT ENABLE (ERROR) operates in conjunction with ENABLE ICD and ENABLE RCD.

| Enable<br>ICD | Enable<br>RCD | interrupt<br>Enable<br>(ERROR) | Interrupt Action            |

|---------------|---------------|--------------------------------|-----------------------------|

| 0             | 0             | . 1                            | Interrupt on TE only        |

| 0             | 1             | ` o                            | Interrupt on UCE or TE      |

| 0             | 1             | 1 %                            | Interrupt on UCE, CE, or TE |

| 1             | 0             | 0                              | Interrupt on UCE or TE      |

| . 1.          | 0             | 1                              | Interrupt on UCE, CE, or TE |

| 1 '           | . 1           | 0                              | Not used                    |

| 1             | 1             | 1                              | Not used                    |

TE = Timing Error, CE = Correctable Error, UCE = Uncorrectable Error.

INTERRUPT ENABLE (NORMAL) (when = 1) enables the BMC to interrupt the host system (via the INT line), when a command execution has been successfully completed (OP COMPLETE = 1 in the STR).

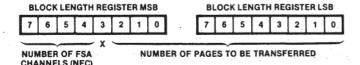

## Block Length Register (BLR) 16 Bits, Write Only

The contents of the block length register determine the system page size and also the number of pages to be transferred in response to a single bubble data read or write command. The bit configuration is as follows:

The system page size is proportional to the number of magnetic bubble memory modules (MBMs) operating in parallel during the data read or write operation. Each MBM requires two FSA channels. Bits 4 through 7 of BLR MSB actually specify the number of FSA channels to be accessed.

The BLR LSB, together with the 3 least significant bits of the BLR MSB, specify the number of pages to be transferred. Up to 2048 pages can be transferred in response to a single bubble data read or write com-

mand, hence the requirement for 11 bits. All 11 bits equal to zero specifies a 2048 page transfer.

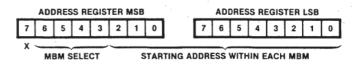

#### Address Register (AR) 16 Bits, Read or Write

The contents of the address register determine which MBM group is to be accessed, and, within that group, what starting address location shall be used in a data read or write operation. The bit configuration is as follows:

Within each MBM there are 8192 possible starting address locations for a data read or write operation, hence the requirement for 13 bits in the starting address.

The selection of the MBMs to be read or written is specified by AR MSB Bits 57. The BMCs interpretation of these bits depends on the number of MBMs in a group, which is specified by BLR MSB Bits 4-7.

Table 6 shows which MBM groups are selected in response to given values for BLR MSB Bits 4-7 and AR MSB Bits 3-6. A 4-megabyte system (8 MBMs) is represented, with the FSA channels numbered 0 through F:

Table 6. Selection of FSA Channels

| AR MSB Bits                                   | BLR MSB Bits (7,6,5,4)          |                          |                    |        |        |  |  |  |

|-----------------------------------------------|---------------------------------|--------------------------|--------------------|--------|--------|--|--|--|

| (7,6,5)                                       | 0000                            | 0001                     | 0010               | 0100   | 1000   |  |  |  |

| 000<br>001<br>010<br>011<br>100<br>101<br>110 | 0<br>1<br>2<br>3<br>4<br>5<br>6 | 0,1<br>2,3<br>4,5<br>6,7 | 0,1,2,3<br>4,5,6,7 | 0 to 7 | 0 to 7 |  |  |  |

Table 5. 4Mbyte System Page Size, Page Address Range, and Data Transfer Performance Configuration

| Γ | В   | LR | MS | SB NFC |    | System Page Size | # of Pages | Address Range  | MBM Data Transfer Rate |

|---|-----|----|----|--------|----|------------------|------------|----------------|------------------------|

| 7 | 7   | 6  | 5  | 4      |    |                  |            |                |                        |

|   | 0   | 0  | 0  | 1      | 2  | 64 byte          | 64K        | 0000 — FFFF    | 25K bytes/sec          |

|   | 0   | 0  | 1  | 0      | 4  | 128 byte         | 32K        | 0000 — 7 F F F | 50K bytes/sec          |

| ( | 0   | 1  | 0  | 0      | 8  | 256 byte         | 16K        | 0000 — 3 F F F | 100K bytes/sec         |

| Ŀ | 1 - | 0  | 0  | 0      | 16 | 512 byte         | 8K         | 0000 — 1 F F F | 200K bytes/sec         |

## FIFO Data Buffer (FIFO) 40 × 8 Bits, Read or Write

The BMC FIFO is a 40-byte buffer through which data passes on its way from the FSAs to the user, or from the user to the FSAs. The FIFO allows the data transfer to proceed in an asynchronous and flexible manner, and relaxes timing constraints, both to the FSAs and also to the user's equipment. The user's system must, however, meet the data rate requirements. When the BMC is busy (executing a command) the FIFO functions as a data buffer. When the BMC is not busy, the FIFO is available to the user as a general purpose FIFO.

#### **FUNCTIONAL OPERATION**

The IC components used in the bubble memory systems have been designed with transparency in mind—that is, a maximum number of operations are handled by the hardware and firmware of these components.

Each four Megabit Bubble Memory (MBM) operates in its own domain, and is unaffected by the number of bubble memories in the system. The roles played by the MBM's immediate support circuitry can be described as if the system contained only one MBM module.

## Data Flow Within the Magnetic Bubble Memory (MBM) System (Single MBM Systems)

During a read operation, data flows as follows: The data from the MBM is input to the Formatter/Sense Amplifier (FSA). Data from each channel (A channel or B channel) of the MBM goes to the corresponding channel of the FSA. In the FSA, the data is paired up with the corresponding bit in the FSA's bootloop register to deter-

mine whether it represents data from a 'good' loop. If it does, the data bit is stored in the FSA FIFO. Error detection and correction is applied to each block of 256 data bits.

From the FSA FIFO, data is sent to the bubble memory controller (BMC) in the form of a serial bit stream, via a one-line bidirectional data bus (DIO). The data is multiplexed onto the DIO line, with data bits coming alternately from the A and B channels of the FSA. The BMC outputs a SYNC pulse to the SELECT.IN input of the FSA. The FSA responds by placing a data bit from the A channel FIFO on the DIO line. One clock cycle later, a data bit from the B channel FIFO is placed on the DIO line. The BMC continues to output SYNC pulses, once every 20 or 80 clock cycles, each time receiving two data bits in return.

In the BMC, the data undergoes serial-to-parallel conversion, and is assembled into bytes, which are then placed in the BMC FIFO, which can hold 40 bytes of data. From this FIFO, the data bytes are written onto the user interface.

During a write operation, the data flow consists of the corresponding operations in the reverse order.

#### INTERFACING REQUIREMENTS

All communications between the host microprocessor, and the bubble memory is performed through the 7224 BMC. Below the general principles are described, for detailed guidelines please refer to the BPK 75 Manual.

First the hardware interfacing requirements and second the software interfacing requirements are described.

**Table 7. Detailed Command Descriptions**

Initialize The BMC executes the Initialize command by first interrogating the bubble system to determine how many FSAs are present, then reading and decoding the bootloop from each MBM and storing the results in the corresponding FSA's bootloop register. All the parametric registers must be properly set up before issuing the Initialize command. Read Bubble Data The Read Bubble Data command causes data to be read from the MBMs into the BMC FIFO. The selection of the MBMs to be accessed and the starting address for the read operation is specified in the address register (AR). The block length register (BLR) specifies the number of system pages to be read. All the parametric registers must be properly set up before issuing the Read Bubble Data command. Write Bubble Data The Write Bubble Data command causes data to be read from the BMC FIFO and written into the MBMs. The selection of the MBMs to be accessed and the starting address for the write operation is specified in the address register (AR). The block length register (BLR) specifies the number of system pages to be written. All the parametric registers must be properly set up before issuing the Write Bubble Data command. Read Seek The Read Seek command rotates the selected MBMs to a designated page address location. No data transfer occurs. The positioning is such that the next data location available to be read is the specified (in AR) page address plus one. The Read Seek command may be used to reduce latency (access time) in cases where information is available for the user to predict the location of an impending read reference to the MBMs.

**Table 7. Detailed Command Descriptions (Continued)** Write Seek The Write Seek command rotates the selected MBMs to a designated page address location. No data transfer occurs. The positioning is such that the next data location available to be written is the specified (in AR) page address plus one. The Write Seek command may be used to reduce latency (access time) in cases where information is available for the user to predict the location of an impending write reference to the MBMs. The Abort command causes a controlled termination of the command currently being Abort executed by the BMC. The Abort command will be accepted by the BMC (and is typically issued) when the BMC is busy. **MBM Purge** The MBM Purge command clears all BMC registers, counters, and the MBM address RAM. Furthermore, it determines how many FSA channels are present in the system and stores this value in the 7224. The "INITIALIZE" command uses this command as a subroutine. **Read Corrected Data** The Read Corrected Data command causes the BMC to read into the BMC FIFO a 256-bit block of data from the FIFO of each selected FSA channel, after an error has been detected. The data cycles through the error correction network of the FSA. After the data has been read, the FSA reports to the BMC whether or not the error was correctable. The Read Corrected Data command is used only when the system is in error correction mode (ENABLE ICD or ENABLE RCD set in the ER). Software Reset The Software Reset command clears the BMC FIFO and all registers, except those containing initialization parameters. It also causes the BMC to send the Software Reset command to selected FSAs in the system. No reinitialization is needed after this command. Read FSA Status The Read FSA Status command causes the BMC to read the 8-bit status register of all FSAs, and to store this information in the BMC FIFO. The Read FSA Status command is independent all parametric registers. Read Bootloop The Read Bootloop Register command causes the BMC to read the bootloop register of the Register selected FSA channels and to store this information in the BMC FIFO. Twenty bytes are transferred for each FSA channel selected. Write Bootloop Proper operation of the FSAs during data transfer to or from the MBMs requires that the Register Masked bootloop register contain exactly 270 logic 1s for each FSA bootloop register. The user may select any subset of 270 "good" loops from the total number of available loops. As an alternative, the Write Bootloop Register Masked command may be used. This command counts the number of logic 1s and masks out the remaining 1s after the proper count has been reached. The Initialize command uses this command as a subroutine. Read Bootloop The Read Bootloop command causes the BMC to read the bootloop from the selected MBM, and to store the decoded bootloop information in the BMC FIFO. The Initialize command uses this command as a subroutine. Write Bootloop The Write Bootloop command causes the existing contents of the selected MBM's bootloop to be replaced by new bootloop data based on 40 bytes of information stored in the FIFO (the user must actually write 41 bytes, where the 41st byte is all 0s). Encoding of the bootloop data is done by the BMC hardware. The Zero Access Read Bubble Data command functions exactly the same as the Read Bubble Zero Access Read Data command except it must be preceded by the Zero Access Read Seek command. The **Bubble Data** parametric registers are written prior to the Zero Access Read Seek command and should not be rewritten for the Zero Access Read Bubble Data command. The Zero Access Read Seek command operates similiarly to the Read Seek command, but it Zero Access Read reads the first page of data from the MBM into the FSA(s) FIFO. This eliminates the first page Seek overhead involved in the Read Bubble Data command. The latency for the first page data is only the time required to read the data from the 7244(s). The values written into the parametric registers prior to the issuance of the Zero Access Read Seek command are identical to those

Bubble Data command.

written for a Read Bubble Data command. The seeking address for the Zero Access Read Seek command is equal to the desired read address. The Zero Access Read Seek command increments the Ad and decrements the BLR. Since the Zero Access Read Bubble Data command expects this increment and decrement, it is used for this data transfer instead of the Read

# HARDWARE INTERFACE REQUIREMENTS User Interface Signals

The source, destination and function of the user interface signals are described in Table 1 in the data sheet.

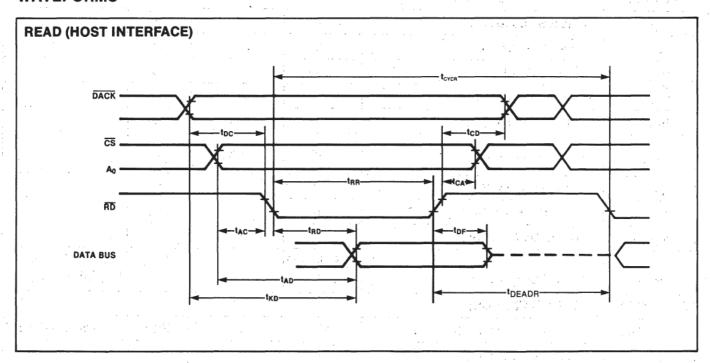

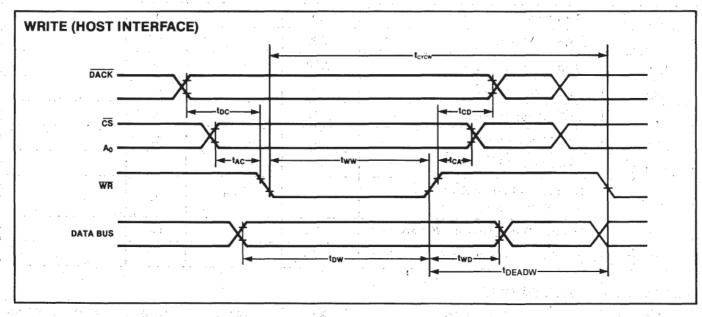

#### **System Timing**

As shown on the timing diagrams in the WAVEFORM section the typical read/write cycle timing provides sufficient tolerance to allow most currently available microprocessors to be easily adapted to the BMC timing requirements.

#### **User Data Transfer Rate Requirements**

The maximum data rate for the user interface is a function of the number of MBMs operated in parallel as outlined in table 8. The rates listed must be considered in relation to the data transfer mode (polled, interrupt-driven, or DMA) to be implemented in order to be sure that the host system software and hardware are capable of keeping up with the data transfer. In other words, the BMC requires the host CPU to be able to sustain the maximum data rate transfer rate for the minimum data transfer (e.g., for a one bubble system keep up the transfer rate for at least 64 bytes = one page).

Table 8. User Data User Transfer Rate Requirements

| Number of<br>MBMs<br>Operating<br>in Parallel | Maximum Data Transfer Rate<br>Between BMC FIFO and the<br>FSAs during Write<br>Bubble Data Commands |

|-----------------------------------------------|-----------------------------------------------------------------------------------------------------|

| 1                                             | 12.5 kbytes/second                                                                                  |

| 2                                             | 25 kbytes/second                                                                                    |

| 4                                             | 50 kbytes/second                                                                                    |

| 8                                             | 100 kbytes/second                                                                                   |

#### **Hardware Interfacing for Data Transfer**

The BMC supports three data transfer modes, i.e. DMA, interrupt-driven and polled.

To support DMA, a hardware mechanism is required for servicing the BMC's data transfer requests. While several hardware implementations are possible, one common configuration is the Intel 8257 DMA controller.

To support an interrupt-driven system an Intel 8259 Programmable Interrupt Controller is often used.

The polled data transfer mode relies almost exclusively on the software interaction between the host processor and the BMC to control the transfer of data.

#### Multiple MBM-System

A BMC is capable of processing data and of supplying the required timing and control signals for operating up to eight Bubble Storage Units (BSUs), each of which is capable of storing 512 kbytes of user data. A BSU consists of a 512 kbyte MBM and its five immediate IC support chips (i.e. a BPK 74 Kit).

#### SOFTWARE INTERFACE REQUIREMENTS

To use the BMC, the user has to write a "bubble memory software driver".

The bubble driver is responsible for all the system interaction with the bubble memory controller and is intrinsic to the efficient and reliable operation of the bubble system. The driver accepts bubble memory commands and command execution parameters from the application program, controls and monitors command execution, and returns operational status information to the application program at command completion. To perform all of these operations, the bubble driver must support the bit/byte level of the bubble memory controller's command and status registers and the parametric registers that define the operating mode, system configuration, and extent of the transfer.

The level of the software driver complexity is a function of the specific application needs. Regardless, a set of basic drivers must be developed that in turn are integrated into a system at the appropriate level. If an application program is small and simple, a basic bubble driver may simply be called from the main program.

At the highest level of driver sophistication, the application program treats the bubble system as a collection of named data areas of files similar to the way in which data is stored and retrieved in disk operating systems. At the file system level, an application program can ignore the mechanics of bubble storage and access and merely present a file name to the driver to open, read, or write, then close the desired bubble file.

#### **Data Organization**

From a software viewpoint, data logically is organized into blocks of bytes called pages. During data transfer operations, one or more of these pages are transferred between the bubble(s) and the host microprocessor. A page is the smallest increment of data that can be transferred; single bytes cannot be transferred. Conceptually, the data organization within a bubble memory is analogous to a disk system. Just as disk sector sizes are fixed when a disk is formatted, bubble page sizes are established, under software control when the bubble system is initialized.

For single bubble system, the page size is fixed at 64 bytes with error correction. The total number of pages available is 8092. In systems with multiple bubbles, page size can vary from 64 bytes to 512 bytes depending on the number of bubble devices in the system. Page size is directly proportional to the system data rate and also determines the total number of available pages (address field size). The selection of the appropriate page size depends primarily on the data rate supported by the system. The higher the data rate, the faster the microprocessor must respond to the demands of the bubble memory controller.

#### **Buffering**

The bubble memory controller includes a FIFO data buffer that, although only 40 bytes long, reconciles timing differences between the parallel data transfer to or from the host microprocessor and the serial data transfer to or from the Bubble Memory Subsystem. Accordingly, when an application program requests data from a bubble, the software driver is responsible for keeping up with the FIFO for the duration of the data transfer in order to prevent the FIFO from overflowing or underflowing.

#### **Command Execution**

Command execution can be performed either in an interrupt driven mode or in a polled mode irrespective of the data transfer mode (polled, interrupt-driven, or DMA).

#### **Data Transfer Mode**

As described earlier in the hardware section, three data transfer modes are available (polled, interrupt-driven or DMA).

System performance, additional hardware and software overhead are all important considerations when choosing the appropriate mode for your application.

#### **Error Correction**

The bubble memory has a built-in error detection. Three levels of error correction are available.

#### Communication with the BMC

All communications between the host and the bubble memory actually are performed through the BMC. The BMC has two input/output (I/O) ports, an eight-bit bidirectional data port, and an eight-bit command/status port. Conceptually, a bubble memory system can be thought of as a disk system in that data in the bubble memory is organized into blocks called pages in bubble technology that are similar to disk sectors. Information such as starting page location, direction of transfer, and the number of pages to be transferred is passed to the BMC before the desired read or write operation is initiated.

The general procedure for communicating with the BMC is:

Set-up the BMC for data transfer communication by loading specific parameters in user-accessible registers.

Send the desired command.

Read the status register to determine if command is accepted.

If applicable, transfer (i.e., read or write) data.

Read the status register until BMC is not busy (or under some conditions "INT" pin).

Examine the status register to determine whether the operation was successful.

For all details and exceptions to this general description consult the BPK 75 User's Manual. (Available 1st Quarter 1984).

#### ABSOLUTE MAXIMUM RATINGS

Temperature under bias ...... -40 to +100°C

Storage Temperature ..... -65°C to +150°C

All Input or Output Voltages and

VCC Supply Voltage ..... -0.5V to 7V

\*NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### D.C. CHARACTERISTICS

$(T_A = 0 \text{ to } 70^{\circ}\text{C}, V_{CC} = 5.0\text{V} + 5\%, -10\%)$

| Symbol             | Parameter                                                                  | Min. | Max.                  | Unit            | Test Condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------|----------------------------------------------------------------------------|------|-----------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>IL</sub>    | Input Low Voltage                                                          |      | 0.8                   | 5 / <b>V</b> 33 | and the state                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| V <sub>IH(1)</sub> | Input High Voltage (all but PWR.FAIL)                                      | 2.0  | V <sub>CC</sub> +0.5V | V               | A STATE OF THE STA |

| V <sub>IH(2)</sub> | Input High Voltage (PWR.FAIL)                                              | 2.5  | V <sub>CC</sub> +0.5V | ٧               | `                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| V <sub>OL(1)</sub> | Output Low Voltage (All outputs except DET.ON, BUS.RD, SHIFT.CLK, and SYNC |      | 45                    | V               | I <sub>OL</sub> = 3.2 mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| V <sub>OL(2)</sub> | Output Low Voltage<br>DET.ON, BUS.RD, SHIFT.CLK, SYNC                      |      | .45                   | ٧               | I <sub>OL</sub> = 1.6 mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| V <sub>OH</sub>    | Output High Voltage                                                        | 2.4  |                       | ٧               | $I_{OH} = 400 \mu A$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |